FPGA新起点V1开发板(十)——按键控制LED

文章目录

- 一、实验任务

- 二、代码展示

- 三、管脚分配

一、实验任务

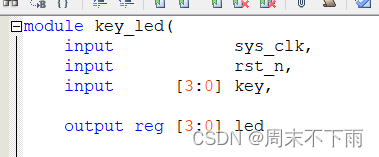

二、代码展示

module key_led(

input sys_clk,

input rst_n,

input [3:0] key,

output reg [3:0] led

);

// reg define

reg [23:0] cnt;

reg [1:0] led_ctrl;

//0.2s计数器

always @ (posedge sys_clk or negedge rst_n) begin

if(!rst_n)

cnt <= 24'd0;

else

if(cnt < 24'd1000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 24'd0;

end

//每隔0.2s改变的四个状态

always @ (posedge sys_clk or negedge rst_n) begin

if(!rst_n)

led_ctrl <= 2'b0;

else

if(cnt == 24'd1000_0000)

led_ctrl <= led_ctrl + 1'b1;

else

led_ctrl <= led_ctrl;

end

//按键控制

always @ (posedge sys_clk or negedge rst_n) begin

if(!rst_n)

led <= 4'b0000;

else

if(key[0] == 1'b0)

case(led_ctrl)

2'd0 : led <= 4'b1000;

2'd1 : led <= 4'b0100;

2'd2 : led <= 4'b0010;

2'd3 : led <= 4'b0001;

endcase

else if(key[1] == 1'b0)

case(led_ctrl)

2'd0 : led <= 4'b0001;

2'd1 : led <= 4'b0010;

2'd2 : led <= 4'b0100;

2'd3 : led <= 4'b1000;

endcase

else if(key[2] == 1'b0)

case(led_ctrl)

2'd0 : led <= 4'b1111;

2'd1 : led <= 4'b0000;

2'd2 : led <= 4'b1111;

2'd3 : led <= 4'b0000;

endcase

else if(key[3] == 1'b0)

led <= 4'b1111;

else

led <= 4'b0000;

end

endmodule

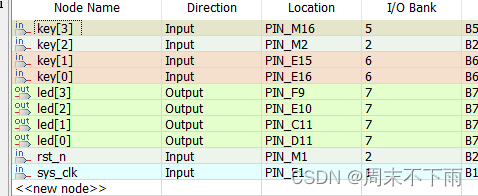

三、管脚分配

感悟

- 可以有下划线

24'd000_0000 - LED是高电平点亮(共阴)

- key是为0时,为按下

key是线网,是根据之后的管脚分配,判断高低电平的,所以不能赋值

led被定义为寄存器,再之后管脚分配,输出高低电平,所以需要赋值,所以是寄存器类型